| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 1/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

# **Product Specification**

To:

Product Name: E102AWF2 R4

Document Issue Date: 2021/3/22

| Customer                                   | InfoVision Optoelectronics |

|--------------------------------------------|----------------------------|

| <u>SIGNATURE</u>                           | <u>SIGNATURE</u>           |

|                                            | REVIEWED BY CQM            |

|                                            |                            |

|                                            |                            |

|                                            | PREPARED BY FAE            |

|                                            |                            |

|                                            |                            |

| Please return 1 copy for your confirmation |                            |

| with your signature and comments.          |                            |

Note: 1. Please contact InfoVision Company before designing your product based on this product.

2. The information contained herein is presented merely to indicate the characteristics and performance of our products. No responsibility is assumed by IVO for any intellectual property claims or other problems that may result from application based on the module described herein.

FQ-7-30-0-009-03D

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 2/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

| Revision | Date       | Page | Revised Content/Summary | Remark |

|----------|------------|------|-------------------------|--------|

| 00       | 2021/03/22 |      | First issued.           |        |

|          |            |      |                         |        |

|          |            |      |                         |        |

|          |            |      |                         |        |

|          |            |      |                         |        |

|          |            |      |                         | 70     |

|          |            |      |                         |        |

|          |            |      |                         |        |

|          |            |      |                         |        |

|          |            |      |                         |        |

|          |            |      |                         |        |

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 3/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

## **CONTENTS**

| 1.0 | GENERAL DESCRIPTIONS       | 4  |

|-----|----------------------------|----|

| 2.0 | ABSOLUTE MAXIMUM RATINGS   | 5  |

| 3.0 | OPTICAL CHARACTERISTICS    | 7  |

| 4.0 | ELECTRICAL CHARACTERISTICS | 12 |

| 5.0 | MECHANICAL CHARACTERISTICS | 36 |

| 6.0 | RELIABILITY CONDITIONS     | 39 |

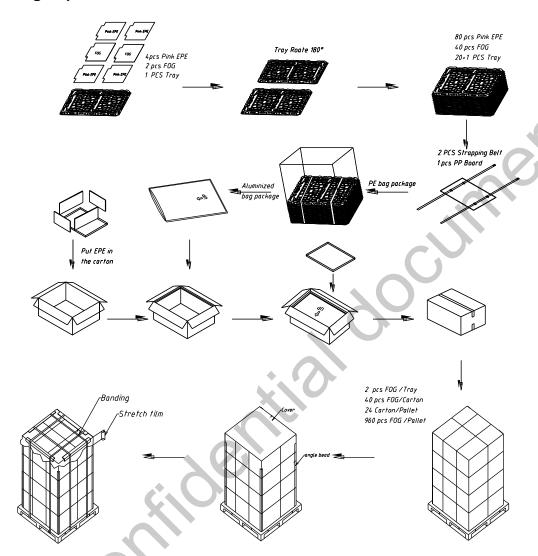

| 7.0 | PACKAGE SPECIFICATION      | 40 |

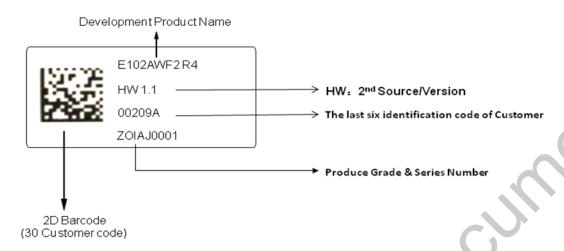

| 8.0 | LOT MARK                   | 41 |

| 9.0 | GENERAL PRECAUTION         | 41 |

Vo.,LTD.

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 4/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

### 1.0 General Descriptions

### 1.1 Introduction

The E102AWF2 R4 is a Color Active Matrix Liquid Crystal Display. The matrix uses a-Si Thin Film Transistor as a switching device. This TFT LCD has a 10.25 inch diagonally measured active display area with FHD resolution (1,920 horizontal by 720 vertical pixels array).

### 1.2 Features

- Supported FHD Resolution

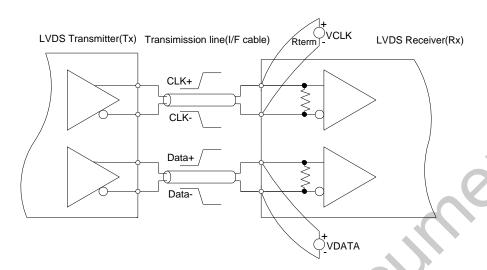

- LVDS Interface

- Wide View Angle

- Compatible with RoHS Standard

1.3 Product Summary

| Items                         | Specifications                           | Unit |

|-------------------------------|------------------------------------------|------|

| Screen Diagonal               | 10.25                                    | inch |

| Active Area (H x V)           | 243.648 x 91.368                         | mm   |

| Number of Pixels (H x V)      | 1,920 x 720                              | -    |

| Pixel Pitch (H x V)           | 0.1269 x 0.1269                          | mm   |

| Pixel Arrangement             | R.G.B. Vertical Stripe                   | -    |

| Display Mode                  | Normally Black                           | -    |

| Contrast Ratio                | 900 (Typ.)                               | -    |

| Response Time                 | 20(Typ.)                                 | ms   |

| Input Voltage                 | 3.3 (Typ.)                               | V    |

| Weight                        | 95 (Max.)                                | g    |

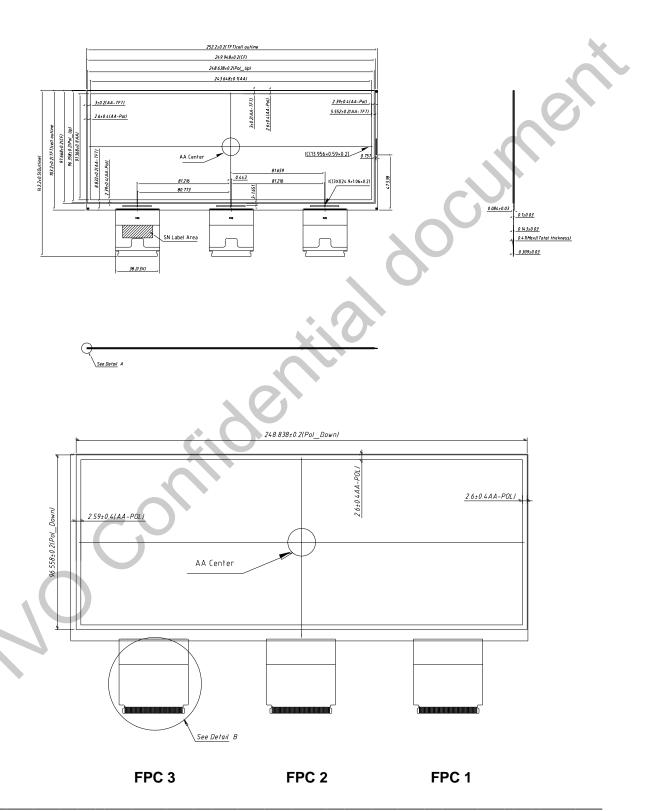

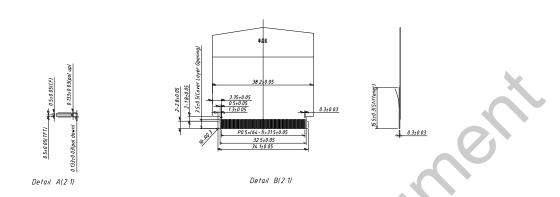

| Outline Dimension (H x V x D) | 252.2 (Typ.) x 103.2(Typ.) x 1.426(Max.) | mm   |

| Electrical Interface (Logic)  | LVDS                                     | -    |

| Support Color                 | 16.7 M (8bit)                            | -    |

| NTSC                          | 68 (Typ.)                                | %    |

| Surface Treatment             | HC                                       | -    |

| Transmittance                 | 3.6(Typ.)                                | %    |

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 5/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

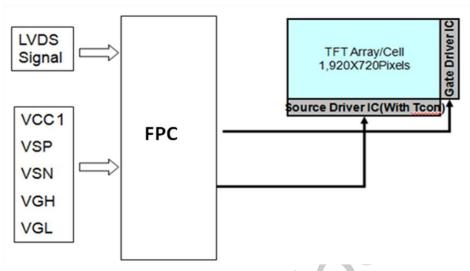

### 1.4 Functional Block Diagram

Figure 1 shows the functional block diagram of the LCD module.

Figure 1 Block Diagram

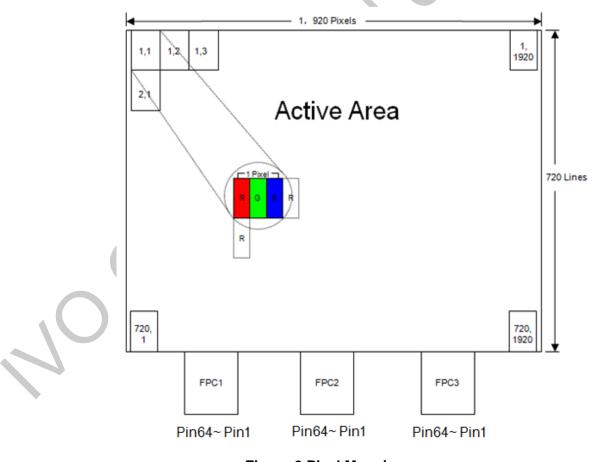

### 1.5 Pixel Mapping

**Figure 2 Pixel Mapping**

### 2.0 Absolute Maximum Ratings

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 6/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

**Table 1 Electrical & Environment Absolute Rating**

| Item                      | Symbol   | Min. | Max.     | Unit       | Note     |

|---------------------------|----------|------|----------|------------|----------|

|                           | VCC1     | -0.3 | 4        | V          |          |

|                           | VSP      | -0.3 | 7.7      | V          |          |

| Power supply voltage      | VSN      | -7.7 | 0.3      | V          | GND=0    |

|                           | VGH      | -0.3 | VGL+42   | V          | (1),(2), |

|                           | VGL      | -25  | 0.3      | V          | (3),(4)  |

| Programming voltage       | VDD_OTP  | -0.3 | 8.8      | V          | (4),(1)  |

| Digital I/O input signals | $V_{IO}$ | -0.3 | VCC1+0.3 | V          |          |

| Operating Temperature     | Tgs      | -20  | 70       | $^{\circ}$ | (1),(2), |

| Storage Temperature       | Ta       | -30  | 85       | $^{\circ}$ | (3),(4)  |

Note (1) All the parameters specified in the table are absolute maximum rating values that may cause faulty operation or unrecoverable damage, if exceeded. It is recommended to follow the typical value.

Note (2) All the contents of electro-optical specifications and display fineness are guaranteed under Normal Conditions. All the display fineness should be inspected under normal conditions. Normal conditions are defined as follow: Temperature:  $25^{\circ}$ C, Humidity:  $55\pm 10\%$ RH.

Note (3) Unpredictable results may occur when it was used in extreme conditions.  $T_a$ = Ambient Temperature,  $T_{gs}$ = Glass Surface Temperature. All the display fineness should be inspected under normal conditions.

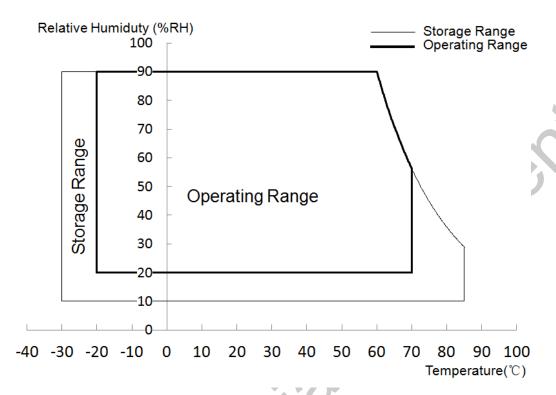

Note (4) Temperature and relative humidity range are shown in the figure below. Wet bulb temperature should be lower than  $57.8^{\circ}$ C, and no condensation of water. Besides, protect the module from static electricity.

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 7/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

Figure 3 Absolute Ratings of Environment of the LCD Module

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 8/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

### 3.0 Optical Characteristics

The optical characteristics are measured under stable conditions as following notes.

**Table 2 Optical Characteristics**

| Item       | Conditions   |                 | Min.  | Тур.  | Max.  | Unit   | Note                    |  |

|------------|--------------|-----------------|-------|-------|-------|--------|-------------------------|--|

| Viewing    | Horizontal   | θ ×+            | 80    | 85    | -     |        | <b>*</b>                |  |

| Angle      | Honzontai    | θ <sub>x-</sub> | 80    | 85    | -     | degree | (1),(2),(3),(6),        |  |

| (CR≥10)    | Vertical     | θ <sub>y+</sub> | 80    | 85    | -     |        | (7)                     |  |

| (ON=10)    | Vertical     | Ө <sub>у-</sub> | 80    | 85    | -     |        |                         |  |

| Contrast   | Center       |                 | 700   | 900   | _     |        | (1),(3),(6),(7)         |  |

| Ratio      | Ochici       |                 | 700   | 300   |       |        | θx=θy=0°                |  |

| Response   | Rising + Fal | ling            |       | 00    | 20    |        | (1),(4),(6),(7)         |  |

| Time       | <b>@25</b> ℃ |                 | -     | 20    | 30    | ms     | θx=θy=0°                |  |

|            |              |                 |       |       |       |        | (1),(5),(7)             |  |

| Transmitta | _            |                 | 3.2   | 3.6   |       | %      | θx=θy=0°                |  |

| nce        |              |                 | 5.2   | 3.0   |       | 70     | (Under                  |  |

|            |              |                 |       | ***   |       |        | C-light)                |  |

|            | Red x        |                 |       | 0.657 |       | -      |                         |  |

|            | Red y        |                 |       | 0.326 |       | -      |                         |  |

| Color      | Green x      |                 | . 0   | 0.289 |       | -      | (1) (5) (7)             |  |

| Chromatici | Green y      |                 | Тур.  | 0.608 | Тур.  | -      | (1),(5),(7)<br>θx=θy=0° |  |

| ty         | Blue x       |                 | -0.02 | 0.132 | +0.02 | -      | (Under                  |  |

| (CIE1931)  | Blue y       | Blue y          |       | 0.143 |       | -      | C-light)                |  |

|            | White x      |                 |       | 0.325 |       | -      | G-light)                |  |

|            | White y      |                 |       | 0.376 |       | -      |                         |  |

| NTSC       | -            |                 | 65    | 68    | -     | %      |                         |  |

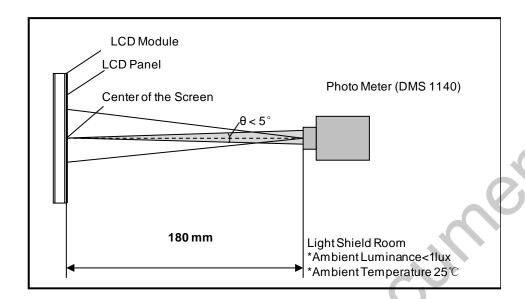

Note (1) Measurement Setup:

The LCD module should be stabilized at given ambient temperature (25°C) for 30 minutes to avoid abrupt temperature changing during measuring. In order to stabilize the luminance, the measurement should be executed after lighting backlight for 30 minutes in the windless room.

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 9/43 |

|----------------|-----------------------------------|------------|-----------|----------|------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00   |

**Figure 4 Measurement Setup**

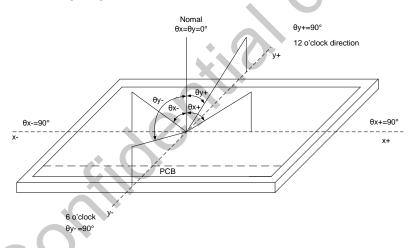

Note (2) Definition of Viewing Angle

**Figure 5 Definition of Viewing Angle**

Note (3) Definition of Contrast Ratio (CR)

The contrast ratio can be calculated by the following expression:

Contrast Ratio (CR) = The luminance of White pattern/ The luminance of Black pattern

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 10/43 |

|----------------|-----------------------------------|------------|-----------|----------|-------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00    |

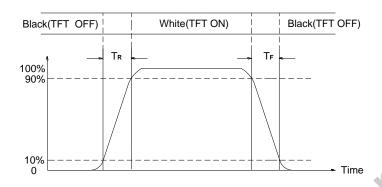

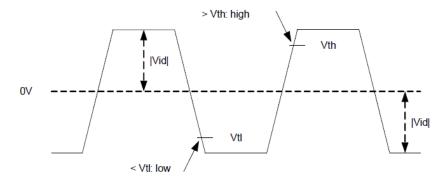

Note (4) Definition of Response Time  $(T_R, T_F)$

**Figure 6 Definition of Response Time**

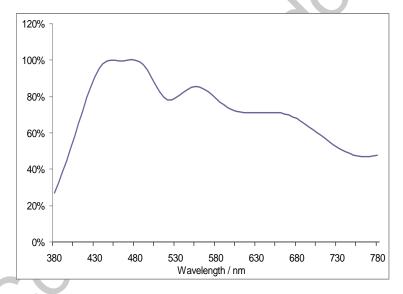

### Note (5) C-Light Spectrum

Figure 7 C-Light Spectrum

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 11/43 |

|----------------|-----------------------------------|------------|-----------|----------|-------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00    |

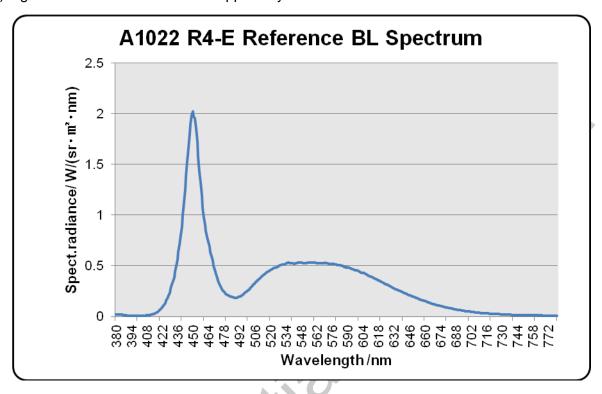

Note (6) Light source is the BL which is supplied by Customer.

Figure 8 Back Light Spectrum

Note (7) All optical data are based on IVO given system & nominal parameter & testing machine in this document.

| Document Title | E102AWF2 R4 Product Specification |            |           | Page No. | 12/43 |

|----------------|-----------------------------------|------------|-----------|----------|-------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00    |

### 4.0 Electrical Characteristics

### **4.1 Interface Connector**

### **Table 3 Signal Connector Type**

| Item                                 | Description                                |

|--------------------------------------|--------------------------------------------|

| Mating Receptacle / Type (Reference) | AORORA F31L-1A7H1-11064-E120 or Compatible |

**Table 4 Signal FPC1 Pin Assignment**

| Pin No. | Symbol | Function                                                           | Remarks |

|---------|--------|--------------------------------------------------------------------|---------|

| 1       | NC     | No connection                                                      | -       |

| 2       | NC     | No connection                                                      | -       |

|         |        | Enable auto reload OTP every 60 frames (Short to FPC2's and        |         |

|         |        | FPC3's ATREN when PCBA design. And when OTP                        |         |

| 3       | ATREN  | programming, ATREN pull L.)                                        | -       |

|         |        | ATREN=H:Enable auto reload OTP(Default)                            |         |

|         |        | ATREN=L:Disable auto reload OTP                                    |         |

| 4       | NC     | No connection                                                      | -       |

| 5       | NC     | No connection                                                      | -       |

| 6       | NC     | No connection                                                      | -       |

| 7       | NC     | No connection                                                      | -       |

| 8       | NC     | No connection                                                      | -       |

|         |        | Power input for LCD common electrode (Require a 2.2uF and          |         |

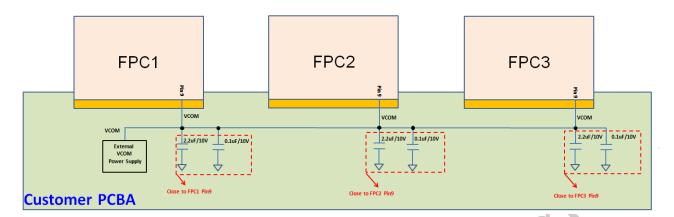

| 9       | VCOM   | 0.1uF capacitor to GND as close to FPC1's VCOM as possible,        | -       |

|         |        | and short to FPC2's and FPC3's VCOM when PCBA design.)             |         |

|         |        | Internal regulator output for negative level shifter (-3V)(Require |         |

| 10      | VCL1   | a 2.2uF capacitor to GND as close to FPC1's VCL1 as                | -       |

|         |        | possible.)                                                         |         |

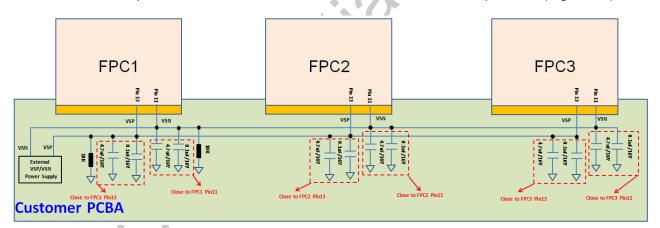

|         |        | Power input for source driver and power circuits (Require a        |         |

| 11      | VSN    | 4.7uF and 0.1uF capacitor and 10KΩ resistance to GND as            |         |

|         | VOIN   | close to FPC1's VSN as possible and Short to FPC2's and            | -       |

|         |        | FPC3's VSN when PCBA design.)                                      |         |

| 12      | GND    | GND                                                                | -       |

|         |        | Power input for source driver and power circuits (Require a        |         |

| 13      | VSP    | 4.7uF and 0.1uF capacitor and 10KΩ resistance to GND as            | -       |

|         |        | close to FPC1's VSP as possible and Short to FPC2's and            |         |

| Document Title | E102AWF2 R4 Product Specification |            |           |          | 13/43 |

|----------------|-----------------------------------|------------|-----------|----------|-------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00    |

|    |         | FPC3's VSP when PCBA design.)                                   |   |

|----|---------|-----------------------------------------------------------------|---|

|    |         | Inversion type selection.                                       |   |

|    |         | H: Dot Inversion                                                |   |

| 14 | INV0    | L: 1+2Dot Inversion                                             | - |

|    |         | Short to FPC2's and FPC3's INV0 when PCBA design. (IVO          |   |

|    |         | suggestion: Please pull L on PCBA)                              |   |

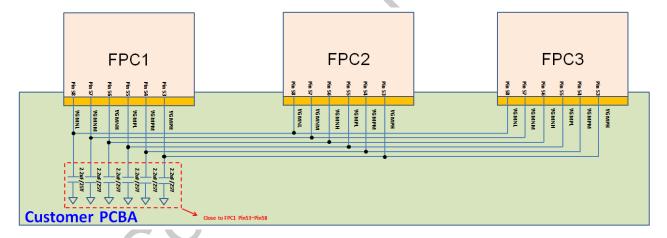

|    |         | Serial Interface clock input (Please Pull H with 14ΚΩ           |   |

| 15 | I2C_SCL | resistance and short to FPC2's and FPC3's I2C_SCL when          |   |

|    |         | PCBA design.)                                                   |   |

|    |         | Serial Interface address and data (Please Pull H with 14ΚΩ      |   |

| 16 | I2C_SDA | resistance and short to FPC2's and FPC3's I2C_SDA when          | - |

|    |         | PCBA design.)                                                   |   |

|    |         | Global Reset pin. Active low(RESETB must meet the               |   |

|    |         | sequence of Driver IC when power on/off ;Add external RC        |   |

| 17 | RESETB  | circuit(R=10KΩ,C= 1uF) to pin RESETB to start whole chip        | - |

|    |         | reset when power up and short to FPC2's and FPC3's              |   |

|    |         | RESETB when PCBA design.)                                       |   |

|    |         | Standby mode setting pin. Active low. Timing controller, output |   |

|    |         | buffer, DAC and power circuit all off when STBYB is             |   |

| 18 | STBYB   | low.(STBYB must meet the sequence of Driver IC when             | - |

|    |         | power on/off; And short to FPC2's and FPC3's STBYB when         |   |

|    |         | PCBA design.)                                                   |   |

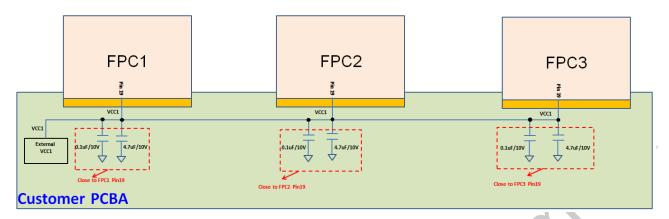

|    |         | Power input for main and I/O power (Require a 4.7uF and         |   |

| 19 | VCC1    | 0.1uF capacitor to GND as close to FPC1's VCC1 as possible      | - |

|    |         | and short to FPC2's and FPC3's VCC1 when PCBA design.)          |   |

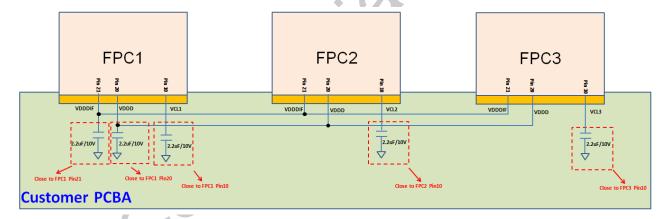

|    |         | Internal regulator output for logic power supply (1.5V)         |   |

| 20 | VDDD    | ( Require a 2.2uF capacitor to GND as close to FPC1's VDDD      | _ |

| 20 | VDDD    | as possible and short to FPC2's and FPC3's VDDD when            |   |

|    |         | PCBA design.)                                                   |   |

|    |         | Internal regulator output for interface power supply            |   |

| 21 | VDDDIF  | (1.5V)(Require a 2.2uF capacitor to GND as close to FPC1's      | _ |

|    |         | VDDDIF as possible and short to FPC2's and FPC3's VDDDIF        |   |

|    |         | when PCBA design.)                                              |   |

| 22 | GND     | GND                                                             | - |

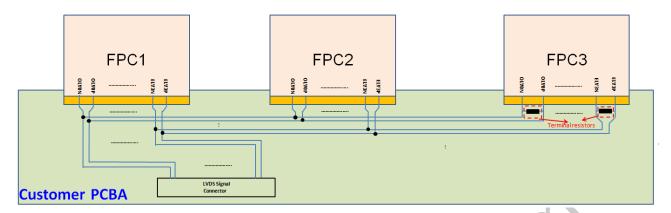

| 23 | ELV3P   | LVDS data lane 3 Positive                                       | - |

| Docum | ent Title | E102AWF2 R4 Pr                | 2 R4 Product Specification |  | Page No. | 14/43 |

|-------|-----------|-------------------------------|----------------------------|--|----------|-------|

| Docum | nent No.  | Issue date 2021/3/22 Revision |                            |  | Revision | 00    |

| 24    | ELV3N     | LVDS data lane 3 Nega         | tive                       |  |          | -     |

| 25    | GND       | GND                           |                            |  |          |       |

| 26    | ELV2P     | LVDS data lane 2 Posit        | ive                        |  |          | -     |

| 27    | ELV2N     | LVDS data lane 2 Nega         | tive                       |  |          | -     |

| 28    | GND       | GND                           |                            |  |          | -     |

| 29    | ELVCLKP   | LVDS Clock Lane Posit         | ive                        |  |          | -     |

| 30    | ELVCLKN   | LVDS Clock Lane Nega          | VDS Clock Lane Negative    |  |          |       |

| 31    | GND       | GND                           | SND                        |  |          |       |

| 32    | ELV1P     | LVDS Data Lane 1 Positive     |                            |  |          | -     |

| 33    | ELV1N     | LVDS Data Lane 1 Negative     |                            |  |          | -     |

| 34    | GND       | GND                           |                            |  |          | -     |

| 35    | ELV0P     | LVDS Data Lane 0 Pos          | itive                      |  |          |       |

| 36    | ELV0N     | LVDS Data Lane 0 Neg          | ative                      |  |          | -     |

| 37    | GND       | GND                           |                            |  |          | -     |

| 38    | OLV3P     | LVDS data lane 3 Posit        | ive                        |  |          | -     |

| 39    | OLV3N     | LVDS data lane 3 Nega         | tive                       |  |          | -     |

| 40    | GND       | GND                           |                            |  |          | -     |

| 41    | OLV2P     | LVDS data lane 2 Posit        | ive                        |  |          | -     |

| 42    | OLV2N     | LVDS data lane 2 Nega         | tive                       |  |          | -     |

| 43    | GND       | GND                           |                            |  |          | -     |

| 44    | OLVCLKP   | LVDS Clock Lane Posit         | ive                        |  |          | -     |

| 45    | OLVCLKN   | LVDS Clock Lane Nega          | tive                       |  |          | -     |

| 46    | GND       | GND                           |                            |  |          |       |

| 47    | OLV1P     | LVDS Data Lane 1 Pos          | itive                      |  |          | -     |

|       | ì         | 1                             |                            |  |          |       |

| Document Title | E102AWF2 R4 Product Specification |            |           |          | 15/43 |

|----------------|-----------------------------------|------------|-----------|----------|-------|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00    |

|      |           | VGMPMO as possible and short to FPC2's and FPC3's              |   |

|------|-----------|----------------------------------------------------------------|---|

|      |           | VGMPMI when PCBA design.)                                      |   |

|      |           | Internal regulator output for positive gamma reference voltage |   |

|      |           | (Require a 2.2uF capacitor to GND as close to FPC1's           |   |

| 55   | VGMPLO    | VGMPLO as possible and short to FPC2's and FPC3's              | - |

|      |           | VGMPLI when PCBA design.)                                      |   |

|      |           | Internal regulator output for negative gamma reference voltage |   |

|      |           | (Require a 2.2uF capacitor to GND as close to FPC1's           |   |

| 56   | VGMNHO    | VGMNHO as possible and short to FPC2's and FPC3's              | - |

|      |           | VGMNHI when PCBA design.)                                      |   |

|      |           | Internal regulator output for negative gamma reference voltage |   |

|      |           | (Require a 2.2uF capacitor to GND as close to FPC1's           |   |

| 57   | VGMNMO    | VGMNMO as possible and short to FPC2's and FPC3's              | - |

|      |           | VGMNMI when PCBA design.)                                      |   |

|      |           | Internal regulator output for negative gamma reference voltage |   |

|      |           | (Require a 2.2uF capacitor to GND as close to FPC1's           |   |

| 58 ' | VGMNLO    | VGMNLO as possible and short to FPC2's and FPC3's              | - |

|      |           | VGMNLI when PCBA design.)                                      |   |

|      | EAU DETA  | Fail detection signal output (Please reserve a test point when |   |

| 59   | FAIL_DET1 | PCBA design.)                                                  | - |

|      |           | Function detection by Hardware/Software selection              |   |

|      |           | FCS=H: Hardware pin                                            |   |

| 60   | FCS       | FCS=L: Software register                                       | - |

|      |           | Short to FPC2's and FPC3's FCS when PCBA design. (IVO          |   |

|      |           | suggestion: Please pull H on PCBA)                             |   |

|      |           | Horizontal shift direction                                     |   |

| 0.4  | D.        | RL=H: Forward(SOUT1→ SOUT2→→SOUT1920)                          |   |

| 61   | RL        | RL=L: Reverse(SOUT1920→SOUT1919→→S1)                           | - |

|      |           | Short to FPC2's and FPC3's RL when PCBA design                 |   |

|      |           | Vertical shift direction(gate output) selection                |   |

| CO   | TD        | TB=H: Forward, Top → Bottom                                    |   |

| 62   | ТВ        | TB=L: Reverse, Bottom → Top                                    | - |

|      |           | Short to FPC2's and FPC3's TB when PCBA design.                |   |

| 00   | DIOTELL   | Enable built-in self test (BIST) function                      |   |

| 63   | BISTEN    | BISTEN=H: BIST mode                                            | - |

|      |           |                                                                |   |

| Document Title | E102AWF2 R4 Pro | oduct Specifica | ıtion     | Page No. | 16/43 |

|----------------|-----------------|-----------------|-----------|----------|-------|

| Document No.   |                 | Issue date      | 2021/3/22 | Revision | 00    |

|    |         | BISTEN=L: Normal mode                                       |     |

|----|---------|-------------------------------------------------------------|-----|

|    |         | (Not use, please leave it to GND)                           |     |

|    |         | Short to FPC2's and FPC3' BISTEN when PCBA design.          |     |

|    |         | Power input for OTP programming (8.6V). Leave this pin open |     |

|    |         | or connect it to VCC1 when not programming OTP (Require a   | A . |

| 64 | VDD_OTP | 2.2uF capacitor to GND as close to FPC1's VDD_OTP as        | - 1 |

|    |         | possible and Short to FPC2's and FPC3's VDD_OTP when        |     |

|    |         | PCBA design.)                                               |     |

### **Table 5 Signal FPC2 Pin Assignment**

| Pin No. | Symbol | Function                                                                                                                          | Remarks |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------|---------|

| 1       | NC     | No connection                                                                                                                     | _       |

| 2       | NC     | No connection                                                                                                                     | -       |

| 3       | ATREN  | Enable auto reload OTP every 60 frames  ATREN=H:Enable auto reload OTP(Default)  ATREN=L:Disable auto reload OTP                  | -       |

| 4       | NC     | No connection                                                                                                                     | -       |

| 5       | NC     | No connection                                                                                                                     | -       |

| 6       | NC     | No connection                                                                                                                     | -       |

| 7       | NC     | No connection                                                                                                                     | _       |

| 8       | NC     | No connection                                                                                                                     | -       |

| 9       | VCOM   | Power input for LCD common electrode (Require a 2.2uF and 0.1uF capacitor to GND as close to FPC2's VCOM as possible.)            | -       |

| 10      | VCL2   | Internal regulator output for negative level shifter (-3V)(Require a 2.2uF capacitor to GND as close to FPC2's VCL2 as possible.) | -       |

| 11      | VSN    | Power input for source driver and power circuits (Require a 4.7uF and 0.1uF capacitor to GND as close to FPC2's VSN as possible.) | -       |

| 12      | GND    | GND                                                                                                                               | -       |

| 13      | VSP    | Power input for source driver and power circuits (Require a 4.7uF and 0.1uF capacitor to GND as close to FPC2's VSP as possible.) | -       |

| Document Title | E102AWF2 R4 Pro | oduct Specifica | ation     | Page No. | 17/43 |

|----------------|-----------------|-----------------|-----------|----------|-------|

| Document No.   |                 | Issue date      | 2021/3/22 | Revision | 00    |

|    |         | Inversion type selection.                                               |     |

|----|---------|-------------------------------------------------------------------------|-----|

| 14 | INV0    | H: Dot Inversion                                                        | -   |

|    |         | L: 1+2Dot Inversion                                                     |     |

| 15 | I2C_SCL | Serial Interface clock input                                            | -   |

| 16 | I2C_SDA | Serial Interface address and data                                       | - 🗶 |

| 17 | RESETB  | Global Reset pin. Active low                                            |     |

| 18 | STBYB   | Standby mode setting pin. Active low. Timing controller, output buffer, |     |

| 10 | SIDID   | DAC and power circuit all off when STBYB is low.                        |     |

| 19 | VCC1    | Power input for main and I/O power (Require a 4.7uF and 0.1uF           | -   |

| 19 | VCC1    | capacitance to GND as close to FPC2's VCC1 as possible.)                |     |

| 20 | VDDD    | Internal regulator output for logic power supply (1.5V)                 | _   |

| 21 | VDDDIF  | Internal regulator output for interface power supply (1.5V)             | -   |

| 22 | GND     | GND                                                                     | -   |

| 23 | ELV3P   | LVDS data lane 3 Positive                                               | -   |

| 24 | ELV3N   | LVDS data lane 3 Negative                                               | -   |

| 25 | GND     | GND                                                                     |     |

| 26 | ELV2P   | LVDS data lane 2 Positive                                               | -   |

| 27 | ELV2N   | LVDS data lane 2 Negative                                               | -   |

| 28 | GND     | GND                                                                     | -   |

| 29 | ELVCLKP | LVDS Clock Lane Positive                                                | -   |

| 30 | ELVCLKN | LVDS Clock Lane Negative                                                |     |

| 31 | GND     | GND                                                                     | -   |

| 32 | ELV1P   | LVDS Data Lane 1 Positive                                               | -   |

| 33 | ELV1N   | LVDS Data Lane 1 Negative                                               | -   |

| 34 | GND     | GND                                                                     | -   |

| 35 | ELV0P   | LVDS Data Lane 0 Positive                                               |     |

| 36 | ELV0N   | LVDS Data Lane 0 Negative                                               | -   |

| 37 | GND     | GND                                                                     |     |

| Document Title | E102AWF2 R4 Product Specification |            | Page No.  | 18/43    |    |

|----------------|-----------------------------------|------------|-----------|----------|----|

| Document No.   |                                   | Issue date | 2021/3/22 | Revision | 00 |

|    | <u> </u>  |                                                                                                  |   |

|----|-----------|--------------------------------------------------------------------------------------------------|---|

| 38 | OLV3P     | LVDS data lane 3 Positive                                                                        | - |

| 39 | OLV3N     | LVDS data lane 3 Negative                                                                        | - |

| 40 | GND       | GND                                                                                              | - |

| 41 | OLV2P     | LVDS data lane 2 Positive                                                                        | - |

| 42 | OLV2N     | LVDS data lane 2 Negative                                                                        | - |

| 43 | GND       | GND                                                                                              | - |

| 44 | OLVCLKP   | LVDS Clock Lane Positive                                                                         | - |

| 45 | OLVCLKN   | LVDS Clock Lane Negative                                                                         | - |

| 46 | GND       | GND                                                                                              |   |

| 47 | OLV1P     | LVDS Data Lane 1 Positive                                                                        | - |

| 48 | OLV1N     | LVDS Data Lane 1 Negative                                                                        | - |

| 49 | GND       | GND                                                                                              | - |

| 50 | OLV0P     | LVDS Data Lane 0 Positive                                                                        | - |

| 51 | OLV0N     | LVDS Data Lane 0 Negative                                                                        | - |

| 52 | GND       | GND                                                                                              | - |

| 53 | VGMPHI    | Positive gamma reference voltage (From FPC1's VGMPHO)                                            | - |

| 54 | VGMPMI    | Positive gamma reference voltage (From FPC1's VGMPMO)                                            | - |

| 55 | VGMPLI    | Positive gamma reference voltage (From FPC1's VGMPLO)                                            | - |

| 56 | VGMNHI    | Negative gamma reference voltage (From FPC1's VGMNHO)                                            | - |

| 57 | VGMNMI    | Negative gamma reference voltage (From FPC1's VGMNMO)                                            | - |

| 58 | VGMNLI    | Negative gamma reference voltage (From FPC1's VGMNLO)                                            | - |

| 59 | FAIL_DET2 | Fail detection signal output(Please reserve a test point when PCBA design.)                      | - |

| 60 | FCS       | Function detection by Hardware/Software selection  FCS=H: Hardware pin  FCS=L: Software register | - |

| 61 | RL        | Horizontal shift direction RL=H: Forward(SOUT1→ SOUT2→→SOUT1920)                                 | - |

| Document Title | E102AWF2 R4 Pro | oduct Specifica | ation     | Page No. | 19/43 |

|----------------|-----------------|-----------------|-----------|----------|-------|

| Document No.   |                 | Issue date      | 2021/3/22 | Revision | 00    |

|    |         | RL=L: Reverse(SOUT1920→SOUT1919→→S1)                           |   |

|----|---------|----------------------------------------------------------------|---|

|    |         | Vertical shift direction(gate output) selection                |   |

| 62 | ТВ      | TB=H: Forward, Top → Bottom                                    | - |

|    |         | TB=L: Reverse, Bottom → Top                                    |   |

|    |         | Enable built-in self test (BIST) function                      |   |

| 63 | DIOTEN  | BISTEN=H: BIST mode                                            |   |

| 63 | BISTEN  | BISTEN=L: Normal mode                                          |   |

|    |         | (Not use, please leave it to GND)                              |   |

|    |         | Power input for OTP programming (8.6V). Leave this pin open or |   |

| 64 | VDD_OTP | connect it to VCC1 when not programming OTP (Require a 2.2uF   | _ |

|    |         | capacitor to GND as close to FPC2's VDD_OTP as possible.)      |   |

| Document Title | E102AWF2 R4 Pro | oduct Specifica | ation     | Page No. | 20/43 |

|----------------|-----------------|-----------------|-----------|----------|-------|

| Document No.   |                 | Issue date      | 2021/3/22 | Revision | 00    |

### **Table 6 Signal FPC3 Pin Assignment**

| Pin No. | Symbol  | Function                                                                | Remarks |

|---------|---------|-------------------------------------------------------------------------|---------|

| 1       | SGOFF2  | The SGOFF1/ SGOFF2 signal control the slow gate off function.           | -       |

|         | 000554  | When they are not used, connecting to GND is recommended.(IVO           |         |

| 2       | SGOFF1  | suggestion: short to GND on PCBA)                                       | -       |

|         |         | Enable auto reload OTP every 60 frames                                  |         |

| 3       | ATREN   | ATREN=H:Enable auto reload OTP(Default)                                 | 4       |

|         |         | ATREN=L:Disable auto reload OTP                                         |         |

|         |         | Slow gate off function control pin. When slow gate off is disabled,     |         |

| 4       | VGN     | connecting VGN to VDD is forbidden, connecting VGN to GND, VGL          | _       |

| •       | 7011    | or VGH, or keeping it floating is recommended. (IVO suggestion:         |         |

|         |         | keep it floating on PCBA)                                               |         |

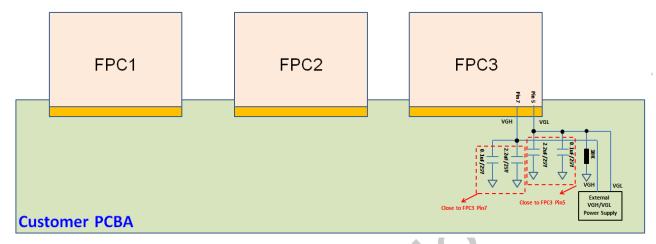

|         |         | Power supply for analog power (Require a 2.2uF and 0.1uF capacitor      |         |

| 5       | VGL     | and 10KΩ resistance to GND as close to FPC3' VGL as possible            | -       |

|         |         | when PCBA design.)                                                      |         |

| 6       | NC      | No connection                                                           | -       |

| 7       | VGH     | Power supply for analog power(Require a 2.2uF and 0.1uF capacitor       | _       |

|         | ۷٥١١    | to GND as close to FPC3's VGH as possible when PCBA design.)            | _       |

| 8       | NC      | No connection                                                           | -       |

| 9       | VCOM    | Power input for LCD common electrode (Require a 2.2uF and 0.1uF         |         |

| 9       | V COIVI | capacitor to GND as close to FPC3's VCOM as possible.)                  | _       |

| 10      | VCL3    | Internal regulator output for negative level shifter (-3V) (Require a   |         |

| 10      | VOLO    | 2.2uF capacitor to GND as close to FPC3's VCL3 as possible.)            | -       |

| 11      | VSN     | Power input for source driver and power circuits (Require a 4.7uF       |         |

| 11      | VSIN    | and 0.1uF capacitor to GND as close to FPC3's VSN as possible.)         | -       |

| 12      | GND     | GND                                                                     | -       |

| 40      | VOD     | Power input for source driver and power circuits (Require a 4.7uF       |         |

| 13      | VSP     | and 0.1uF capacitor to GND as close to FPC3's VSP as possible.)         | -       |

|         |         | Inversion type selection.                                               |         |

| 14      | INV0    | H: Dot Inversion                                                        | -       |

|         |         | L: 1+2Dot Inversion                                                     |         |

| 15      | I2C_SCL | Serial Interface clock input                                            | -       |

| 16      | I2C_SDA | Serial Interface address and data                                       | -       |

| 17      | RESETB  | Global Reset pin. Active low                                            | -       |

| 18      | STBYB   | Standby mode setting pin. Active low. Timing controller, output buffer, | -       |

| Document Title | E102AWF2 R4 Pro | E102AWF2 R4 Product Specification |           |          |    |

|----------------|-----------------|-----------------------------------|-----------|----------|----|

| Document No.   |                 | Issue date                        | 2021/3/22 | Revision | 00 |

| DAC and power circuit all off when STBYB is low.  Power input for main and I/O power (Require a 4.7uF and 0.1uF capacitance to GND as close to FPC3's VCC1 as possible )  10 VDDD Internal regulator output for logic power supply (1.5V)  11 VDDDIF Internal regulator output for interface power supply (1.5V)  12 GND GND  13 ELV3P LVDS data lane 3 Positive  14 ELV3N LVDS data lane 3 Negative  15 GND GND  16 ELV2P LVDS data lane 2 Positive  17 ELV2N LVDS data lane 2 Negative  18 GND GND  19 ELVCLKP LVDS Clock Lane Positive  29 ELVCLKP LVDS Clock Lane Negative  30 ELV7LKN LVDS Data Lane 1 Positive  31 GND GND  32 ELV1P LVDS Data Lane 1 Positive  33 ELV1N LVDS Data Lane 1 Positive  34 GND GND  35 ELVOP LVDS Data Lane 0 Positive  36 ELV0N LVDS Data Lane 0 Positive  37 GND GND  38 OLV3N LVDS data lane 3 Positive  40 GND GND  41 OLV2P LVDS data lane 2 Positive  42 OLV2N LVDS data lane 2 Positive  43 GND GND  44 OLVCLKP LVDS Clock Lane Negative  5 CLVCLKP LVDS Data Lane 1 Positive  6 CLVCLKP LVDS Data Lane 0 Positive  7 GND GND  8 OLV3N LVDS data lane 3 Positive  9 GND  40 GND  41 OLV2P LVDS data lane 2 Positive  42 OLV2N LVDS data lane 2 Positive  43 GND GND  44 OLVCLKP LVDS Clock Lane Negative  45 OLVCLKN LVDS Clock Lane Negative  46 GND GND  47 OLVCLKP LVDS Clock Lane Negative  48 OLVCLKN LVDS Clock Lane Positive  49 OLVCLKN LVDS Clock Lane Positive  40 GND GND  41 OLVCLKP LVDS Clock Lane Negative  43 GND GND  44 OLVCLKP LVDS Clock Lane Negative  45 OLVCLKN LVDS Clock Lane Negative |    |         |                                                             |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|-------------------------------------------------------------|-----|

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |         | DAC and power circuit all off when STBYB is low.            |     |

| capacitance to GND as close to FPC3's VCC1 as possible )  20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19 | VCC1    |                                                             | _   |

| 21         VDDDIF         Internal regulator output for interface power supply (1.5V)         -           22         GND         GND         -           23         ELV3P         LVDS data lane 3 Positive         -           24         ELV3N         LVDS data lane 3 Negative         -           25         GND         GND         -           26         ELV2P         LVDS data lane 2 Positive         -           27         ELV2N         LVDS data lane 2 Negative         -           28         GND         -         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         -         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 3 Positive         -           37         GND         -           38         OLV3P         LVDS data lane 3 Positive                                                                                                                                                                                                                                                                                                                                                                                       |    |         | capacitance to GND as close to FPC3's VCC1 as possible )    |     |

| 22         GND         GND         -           23         ELV3P         LVDS data lane 3 Positive         -           24         ELV3N         LVDS data lane 3 Negative         -           25         GND         GND         -           26         ELV2P         LVDS data lane 2 Positive         -           27         ELV2N         LVDS data lane 2 Negative         -           28         GND         GND         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELVOP         LVDS Data Lane 0 Positive         -           36         ELVON         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           40         GND         -         -                                                                                                                                                                                                                                                                                                                                                                                                                          | 20 | VDDD    | Internal regulator output for logic power supply (1.5V)     | -   |

| 23         ELV3P         LVDS data lane 3 Positive         -           24         ELV3N         LVDS data lane 3 Negative         -           25         GND         GND         -           26         ELV2P         LVDS data lane 2 Positive         -           27         ELV2N         LVDS data lane 2 Negative         -           28         GND         GND         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           40         GND         GND         -           41         OLV2P         LVDS data lane                                                                                                                                                                                                                                                                                                                                                                                                         | 21 | VDDDIF  | Internal regulator output for interface power supply (1.5V) | -   |

| 24         ELV3N         LVDS data lane 3 Negative         -           25         GND         GND         -           26         ELV2P         LVDS data lane 2 Positive         -           27         ELV2N         LVDS data lane 2 Negative         -           28         GND         GND         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 1 Negative         -           36         ELV0N         LVDS Data Lane 0 Positive         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           40         GND         GND         -           40         GND         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative                                                                                                                                                                                                                                                                                                                                                                                                                      | 22 | GND     | GND                                                         | -   |

| 25         GND         GND         -           26         ELV2P         LVDS data lane 2 Positive         -           27         ELV2N         LVDS data lane 2 Negative         -           28         GND         GND         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1P         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           40         GND         -         -           40         GND         -         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS Clock Lane Positive                                                                                                                                                                                                                                                                                                                                                                                                                           | 23 | ELV3P   | LVDS data lane 3 Positive                                   |     |

| 26         ELV2P         LVDS data lane 2 Positive         -           27         ELV2N         LVDS data lane 2 Negative         -           28         GND         GND         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND                                                                                                                                                                                                                                                                                                                                                                                                          | 24 | ELV3N   | LVDS data lane 3 Negative                                   | 7-) |

| 27         ELV2N         LVDS data lane 2 Negative         -           28         GND         GND         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         -         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         - <td>25</td> <td>GND</td> <td>GND</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                            | 25 | GND     | GND                                                         | -   |

| 28         GND         GND         -           29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         - </td <td>26</td> <td>ELV2P</td> <td>LVDS data lane 2 Positive</td> <td>-</td>                                                                                                                                                                                                                                                                                                                              | 26 | ELV2P   | LVDS data lane 2 Positive                                   | -   |

| 29         ELVCLKP         LVDS Clock Lane Positive         -           30         ELVCLKN         LVDS Clock Lane Negative         -           31         GND         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27 | ELV2N   | LVDS data lane 2 Negative                                   | -   |

| 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28 | GND     | GND                                                         | -   |

| 31         GND         GND         -           32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29 | ELVCLKP | LVDS Clock Lane Positive                                    | -   |

| 32         ELV1P         LVDS Data Lane 1 Positive         -           33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30 | ELVCLKN | LVDS Clock Lane Negative                                    | -   |

| 33         ELV1N         LVDS Data Lane 1 Negative         -           34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31 | GND     | GND                                                         | -   |

| 34         GND         GND         -           35         ELV0P         LVDS Data Lane 0 Positive         -           36         ELV0N         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32 | ELV1P   | LVDS Data Lane 1 Positive                                   | -   |

| 35         ELVOP         LVDS Data Lane 0 Positive         -           36         ELVON         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         GND           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33 | ELV1N   | LVDS Data Lane 1 Negative                                   | -   |

| 36         ELVON         LVDS Data Lane 0 Negative         -           37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34 | GND     | GND                                                         | -   |

| 37         GND         GND         -           38         OLV3P         LVDS data lane 3 Positive         -           39         OLV3N         LVDS data lane 3 Negative         -           40         GND         -           41         OLV2P         LVDS data lane 2 Positive         -           42         OLV2N         LVDS data lane 2 Negative         -           43         GND         -           44         OLVCLKP         LVDS Clock Lane Positive         -           45         OLVCLKN         LVDS Clock Lane Negative         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 | ELV0P   | LVDS Data Lane 0 Positive                                   | -   |